Московский государственный технический университет имени Н.Э. Баумана

# Методические указания

# А.Ю. Попов

Лабораторная работа №2

**Проектирование цифровых** устройств на основе ПЛИС

Москва 2014

**Цель работы:** закрепление на практике теоретических сведений, полученных при изучении методики проектирования цифровых устройств на основе программируемых логических интегральных схем (ПЛИС), получение необходимых навыков работы с системой автоматизированного проектирования ISE WebPack 9.1 устройств на основе ПЛИС фирмы Xilinx, изучение аппаратных и программных средств моделирования, макетирования и отладки устройств на основе ПЛИС.

Для выполнения работы студенту необходимо ознакомиться с архитектурой ПЛИС FPGA Spartan 3 производства фирмы Xilinx, изучить методику проектирования устройств на основе ПЛИС с использованием САПР ISE WebPack 9.1, спроектировать и реализовать с помощью набора XC3S200 (или набора Nexys2 на основе ПЛИС XC3E-500) устройство управления счетом и индикацией состояния 16-разрядного счетчика.

#### Описание проектируемого устройства

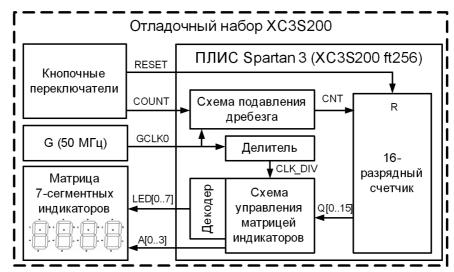

В данной лабораторной работе осваивается методика проектирования цифровых устройств на примере разработки и реализации на ПЛИС схемы управления счетом и индикацией состояния 16-разрядного счетчика. Отладка устройства производится с помощью набора XC3S200 (или набора Nexys2 на основе ПЛИС XC3E-500 с аналогичными функциями), который содержит матрицу 7-сегментных индикаторов и кнопки, необходимые для управления разрабатываемым устройством. Выбор набора (XC3S200 или Nexys2) определяется в соответствии с вариантом в таблице 1 (см. далее). Состав устройства и назначение используемых ресурсов отладочного набора XC3S200 показаны на рисунке 1 (набор Nexys2 содержит аналогичные ресурсы).

Рисунок 1 – Использование отладочного набора XC3S200 для реализации схемы управления и индикацией 16-ти разрядного счетчика

В устройстве используется синхронный 16-разрядный счетчик с асинхронным сбросом. Для управления счетом и сбросом используются две кнопки, входящие в состав отладочного набора (линии RESET и COUNT). При этом учитывается, что подача внешнего сигнала управления счетом COUNT непосредственно на вход синхронизации счетчика привела бы к многочисленным ложным срабатываниям из-за наличия дребезга при замыкании и размыкании кнопки. Для устранения этого в работе используется схема подавления дребезга, выдающая на счетчик сигнал CNT.

Состояние 16-разрядного счетчика передается на схему управления матрицей индикаторов, которая обеспечивает мультиплексированную передачу тетрад данных на декодер 7-сегментого кода, а также сопровождает выдачу данных сигналами управления анодами (A[0..3]). На выходе декодера формируется код активизации сегментов (LED[0..7]), передаваемый непосредственно на 4 индикатора, входящие в состав отладочного набора. Делитель частоты должен выдавать сигнал синхронизации CLK\_DIV низкой частоты (100-200 Гц) на схему управления матрицей индикаторов.

#### Разработка схемы подавления дребезга

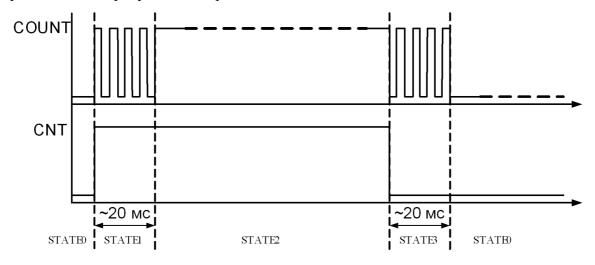

Схема подавления дребезга представляет собой автомат, воспринимающий входной сигнал COUNT от кнопки и выдающий выходной сигнал CNT в соответствии с приведенной на рисунке 2 диаграммой.

Рисунок 2 – Диаграмма работы схемы подавления дребезга

Кнопки, имеющиеся в наличие на плате XC3S200 или Nexys2, обладают дребезгом и не снабжены схемами их подавления (триггерами Шмидта и т.д.). Как при нажатии, так и при отпускании кнопки происходит многократное изменение уровня напряжения на линии COUNT, вызванное упругими соударениями. Для предотвращения

нежелательных многократных срабатываний устройств, следует построить схему, исключающую возможность прохождения сигналов в момент дребезга. Это можно осуществить с помощью дополнительного счетчика, исполняющего роль схемы задержки на длительность переходных процессов. При подаче на вход данного счетчика сигнала отладочного набора GCLKO, имеющего частоту 50 МГц, в качестве информационного сигнала окончания счета может быть использовано значение двадцатого разряда счетчика(Q[20]). Разрешение работы счетчика задается высоким уровнем сигнала CNT\_EN. После окончания счета необходимо выполнить сброс счетчика в исходное нулевое состояние сигналом CNT\_CLR.

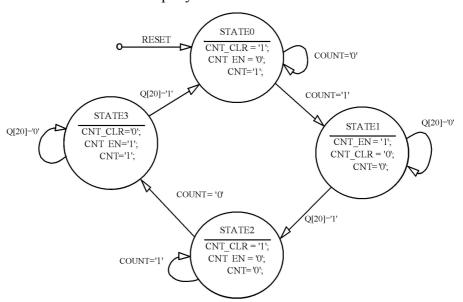

Автомат, реализующий указанную логику работы, может находиться в одном из четырех состояний: ожидания нажатия (STATE0), счет времени после нажатии (STATE1), ожидание отпускания (STATE2), счет времени после отпускания (STATE3). Диаграмма переходов состояния показана на рисунке 3.

Рисунок 3 – Диаграмма состояния автомата подавления дребезга

**Задание 1.** Выполнить кодирование состояний автомата, представленного на рисунке 3, в соответствии с индивидуальным вариантом из таблицы 1. Для этого заполнить таблицу 2.

| Таблина 1 - | - Индивидуальные варианты коди        | повяния состояний явтомятя |

|-------------|---------------------------------------|----------------------------|

| т аолица т  | HIIIAHDHA (AMBIIDIC DADHAII I DI KOAH | pobanna cocionnan abiomaia |

| Вариант: | Набор   | Двоичный код состояния ( $\mathbf{Q}_1\mathbf{Q}_0$ ) |        |        |        |  |

|----------|---------|-------------------------------------------------------|--------|--------|--------|--|

|          |         | State0                                                | State1 | State2 | State3 |  |

| 1        | XC3S200 | 00                                                    | 01     | 10     | 11     |  |

| 2        | XC3S200 | 00                                                    | 01     | 11     | 10     |  |

| 3        | Nexys 2 | 00                                                    | 10     | 01     | 11     |  |

| Вариант: | Набор   | Двоичный код состояния (Q₁Q₀) |        |        |        |  |  |

|----------|---------|-------------------------------|--------|--------|--------|--|--|

|          |         | State0                        | State1 | State2 | State3 |  |  |

| 4        | XC3S200 | 00                            | 10     | 11     | 01     |  |  |

| 5        | XC3S200 | 00                            | 11     | 10     | 01     |  |  |

| 6        | Nexys 2 | 00                            | 11     | 01     | 10     |  |  |

| 7        | XC3S200 | 01                            | 00     | 10     | 11     |  |  |

| 8        | XC3S200 | 01                            | 00     | 11     | 10     |  |  |

| 9        | Nexys 2 | 01                            | 10     | 00     | 11     |  |  |

| 10       | XC3S200 | 01                            | 10     | 11     | 00     |  |  |

| 11       | XC3S200 | 01                            | 11     | 00     | 10     |  |  |

| 12       | Nexys 2 | 01                            | 11     | 10     | 00     |  |  |

| 13       | XC3S200 | 10                            | 00     | 01     | 11     |  |  |

| 14       | XC3S200 | 10                            | 00     | 11     | 01     |  |  |

| 15       | Nexys 2 | 10                            | 01     | 00     | 11     |  |  |

| 16       | XC3S200 | 10                            | 01     | 11     | 00     |  |  |

| 17       | XC3S200 | 10                            | 11     | 00     | 01     |  |  |

| 18       | Nexys 2 | 10                            | 11     | 01     | 00     |  |  |

| 19       | XC3S200 | 11                            | 00     | 01     | 10     |  |  |

| 20       | XC3S200 | 11                            | 00     | 10     | 01     |  |  |

| 21       | Nexys 2 | 11                            | 01     | 00     | 10     |  |  |

| 22       | XC3S200 | 11                            | 01     | 10     | 00     |  |  |

| 23       | XC3S200 | 11                            | 10     | 00     | 01     |  |  |

| 24       | Nexys 2 | 11                            | 10     | 01     | 00     |  |  |

По таблице выходов 2 определить функции сигналов управления: CNT = f(Q1,Q0), CNT\_EN = f(Q1,Q0), CNT\_CLR = f(Q1,Q0). Результаты занести в отчет.

Таблица 2 – Таблица выходов

| Состояние                     | State0 | State1 | State2 | State3 |

|-------------------------------|--------|--------|--------|--------|

| Двоичный код состояния (Q1Q0) |        |        |        |        |

| CNT                           | 0      | 1      | 1      | 0      |

| CNT_EN                        | 0      | 1      | 0      | 1      |

| CNT_CLR                       | 1      | 0      | 1      | 0      |

Синтезировать схему автомата с использованием динамических синхронных Dтриггеров с асинхронным сбросом и установкой (элементы FDC и FDP библиотеки) и шестнадцатиразрядных счетчиков (элемент CR16CE), управляемых фронтом сигнала синхронизации СLК. Для определения функций D0=f(Q[20],COUNT,Q1,Q0) и D1=f(Q[20],COUNT,Q1,Q0) заполнить таблицу 3. Результаты занести в отчет.

Таблица 3 – Сигналы D1 и D2

| COUNT | Q[20] | Q1(t) | Q0(t) | Q1(t+1) | Q0(t+1) | D1 | D0 | Описание события         |

|-------|-------|-------|-------|---------|---------|----|----|--------------------------|

| 0     | X     |       |       |         |         |    |    | Ожидание нажатия кнопки  |

| 1     | X     |       |       |         |         |    |    | Нажатие кнопки           |

| х     | 0     |       |       |         |         |    |    | Ожидание окончания счета |

| X     | 1     |       |       |         |         |    |    | Конец счета              |

| 1     | X     |       |       |         |         |    |    | Ожидание отпускания      |

| 0     | X     |       |       |         |         |    |    | Отпускание кнопки        |

| х     | 0     |       |       |         |         |    |    | Ожидание окончания счета |

| х     | 1     |       |       |         |         |    |    | Конец счета              |

**Задание 2.** Собрать модель полученного устройства в редакторе схем САПР ISE WebPack 9.1. Для этого выполнить следующие действия:

- Запустить САПР ISE WebPack 9.1.

- В меню File выбрать пункт New Project.

- Указать название и путь к файлу создаваемого проекта.

- Указать тип модуля верхнего уровня: Schematic. Нажать кнопку Next.

- В поле Product Category указать: All.

- В поле Family указать: Spartan3 для набора XC3S200 или Spartan3E для набора Nexys2.

- В поле Device указать: XC3S200 для набора XC3S200 или XC3E500 для набора Nexys2.

- В поле Package указать: FT256 для набора XC3S200 или FG320 для набора Nexys2.

- В поле Speed указать: -5.

- В поле Synthesis Tool указать: XST(VHDL/Verilog).

- В поле Simulator указать: ISE Simulator (VHDL/Verilog).

- В поле Preferred Language: VHDL. Трижды нажать кнопку Next, Нажать кнопку Finish.

• Создать новое схемотехническое описание проекта, выбрав в меню Project пункт New Source. Далее выбрать тип описания (Schematic) и указать имя и путь к создаваемому файлу описания. Нажать кнопки Next и Finish.

В итоге будет создан и открыт для редактирования файл схемотехнического описания. Для описания схемы необходимо поместить на рабочее поле компоненты, выбрав их во вкладке Symbols окна Sources. В данном задании потребуются компоненты FDC, FDP, CR16CE, AND, OR, VCC, GND.

Соединение компонентов выполняется с помощью цепей и шин. Для создания цепи или шины необходимо над рабочим полем вызвать контекстное меню с помощью правой кнопки мыши. Далее, в контекстном меню выбрать пункт Add и подпункт Wire. Если порт компонента является шиной, то цепь также будет иметь такой тип.

Для подключения цепи или группы цепей к существующей шине используется разветвитель Виз Тар. Для его добавления в контекстном меню выбрать пункты Add и Виз Тар, после чего необходимо поместить разветвитель на шине. Указание соответствия цепей в шине с цепями, подведенными к разветвителю, выполняется с помощью имен. Например, если шина носит имя XLXN\_1(15:0), то для выбора старшей цепи следует назвать подведенную к разветвителю цепь, как XLXN\_1(15). Порты схемы подключаются к цепям с помощью компонента I/O Marker. Для этого в контекстном меню необходимо выбрать пункты Add и I/O Marker.

**Задание 3.** В интегрированном редакторе тестов САПР ISE WebPack 9.1 разработать тест для полученного устройства и выполнить моделирование его работы в ISE Simulator.

Для этого необходимо создать новое описание теста проекта, выбрав в меню Project пункт New Source. Далее выбрать тип описания (Test Bench WaveForm) и указать имя и путь к создаваемому файлу теста. Далее нажать на кнопку Next и в открывшемся диалоге выбрать тестируемое описание, после чего нажать на кнопки Next и Finish. В результате будет создан файл графического тестового воздействия для выбранного описания и будет вызван диалог его настройки. В этом диалоге необходимо указать сигнал синхронизации (например, CLK) и время тестирования в поле Initial Length of Test Bench (остальные параметры можно оставить неизменными).

После создания теста и его сохранения можно приступать к моделированию, для чего активизировать вкладку Sources в окне Sources. В выпадающем списке Sources For выбрать строку Behavioral Simulation и выбрать запускаемый тест в дереве описаний

проекта. После этого во вкладке Processes окна Processes выбрать пункт Xilinx ISE Simulator и пункт Simulate Behavioral Model.

Схему устройства и результаты моделирования занести в отчет.

#### Разработка схемы управления 7-сегментными индикаторами

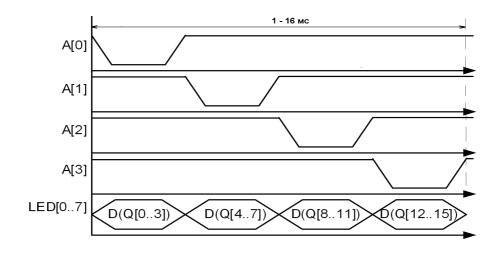

Для индикации информационных сигналов большой разрядности при отладке устройств с помощью набора XC3S200 или набора Nexys2 целесообразно использовать имеющиеся четыре 7-сегментных индикатора. Управление их работой осуществляется благодаря подаче восьми общих сигналов управления сегментами одновременно с установкой в активный низкий уровень сигнала выборки анода А[0..3]. Таким образом, состояние линий LED должно устанавливаться схемой управления в соответствии с активным в данный момент 7-сегментным индикатором. Диаграмма работы устройства управления четырьмя 7-сегментными индикаторами показана на рисунке 4. Четыре тетрады сигналов данных (Q[0..3], Q[4..7], Q[8..11], Q[12..15]) должны быть преобразованы в код активизации индикаторов с помощью декодера. Темп активизации индикаторов должен обеспечивать отсутствие видимого мерцания сегментов (100-200 Гц). Для задания частоты активизации CLK DIV целесообразно использовать дополнительный 16-разрядный счетчик – делитель частоты СВ16СЕ, соединенный по CEO с буфером разрешения синхросигнала BUFGCE (период активизации четырех индикаторов должен составлять от 1 до 16 мс, частота от 1КHz до 60 Hz).

Рисунок 4 – Диаграмма работы устройства управления четырьмя 7-сегментными индикаторами

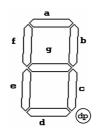

Рисунок 5 - Назначение сегментов индикатора

преобразования четырех информационных сигналов В код активизации светодиодов восьми используется табличное перекодирование, реализуемое программой LUТ-таблиц. синтеза при помощи Расположение сегментов индикатора показано на рисунке 5, а коды их активизации для различных значений входного четырехразрядного слова D[0..3] указаны в таблице 4 (нулевой разряд означает активизацию сегмента; сегмент DP не активизируется).

Таблица 4 – Значения информационных входов активизации сегментов 7-сегментного индикатора для возможных значений информационного слова D[0..3]

| D[03] | DP | A | В | С | D | E | F | G |

|-------|----|---|---|---|---|---|---|---|

| 0000  | 1  | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0001  | 1  | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 0010  | 1  | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0011  | 1  | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 0100  | 1  | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 0101  | 1  | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0110  | 1  | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0111  | 1  | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1000  | 1  | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1001  | 1  | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1010  | 1  | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1011  | 1  | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1100  | 1  | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 1101  | 1  | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1110  | 1  | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1111  | 1  | 0 | 1 | 1 | 1 | 0 | 0 | 0 |

Задание 4. Разработать устройство управления, принимающее 16-разрядное информационное слово Q[0..15] и управляющее их последовательной выдачей по шине D[0..3] на декодер 7-сегментных индикаторов в соответствии с показанной на рисунке 4 диаграммой. Для этого создать файл VHDL, содержащий следующий текст описания:

```

LIBRARY ieee;

USE ieee.std logic 1164.ALL;

USE ieee.std logic arith.ALL;

ENTITY Seven Segment Driver IS

PORT (

clk_div : IN std_logic;

Q : IN std_logic_vector(15 DOWNTO 0);

rst : IN std_logic;

D : OUT std_logic_vector(3 DOWNTO 0);

A : INOUT std_logic_vector(3 DOWNTO 0));

END ENTITY Seven Segment Driver;

ARCHITECTURE Struct OF Seven Segment Driver IS

A drive: PROCESS (clk div, rst)

BEGIN

IF (rst = '1') THEN

A<="1110";

ELSIF (clk div'EVENT AND clk div='1') THEN

A(3) \le A(2);

A(2) \le A(1);

A(1) \le A(0);

A(0) \le A(3);

END IF;

END PROCESS A drive;

D(0) \ll Q(0) AND NOT (A(0))

OR (Q(4) AND NOT(A(1))

OR (Q(8) AND NOT(A(2))

OR (Q(12) \text{ AND NOT}(A(3)));

D(1) \le (Q(1) \text{ AND NOT}(A(0)))

OR (Q(5) AND NOT(A(1))

OR (Q(9) AND NOT(A(2))

OR (Q(13) \text{ AND NOT}(A(3)));

D(2) \le (Q(2) \text{ AND NOT}(A(0)))

OR (Q(6) AND NOT(A(1))

OR (Q(10) \text{ AND NOT}(A(2)))

OR (Q(14) \text{ AND NOT}(A(3)));

D(3) \le (Q(3) \text{ AND NOT}(A(0)))

OR (Q(7) AND NOT(A(1))

OR (Q(11) AND NOT(A(2))

OR (Q(15) AND NOT(A(3)));

END ARCHITECTURE Struct;

```

В интегрированном редакторе тестов CAПР ISE WebPack 9.1 разработать тест для полученного устройства и выполнить моделирование его работы в ISE Simulator. Описание устройства и результаты моделирования занести в отчет. Подключить устройство к текущему проекту, выбрав в меню Project пункт Add Source.

Задание 5. Разработать поведенческое VHDL описание схемы преобразования четырехразрядного информационного кода D[0..3] в код активизации 7-сегментного индикатора LED[0..7] в соответствии с таблицей 4. Подключить устройство к библиотеке компонентов текущего проекта. Текст описания занести в отчет.

## Разработка и отладка основного модуля проекта

Для реализации частей разработанного устройства и последующей их отладки необходимо создать файл ограничений, содержащий назначение контактов целевой микросхемы. Вариант назначения сигналам контактов микросхемы, расположенной на плате набора XC3S200, представлены в таблице 5.

Таблица 5 – Вариант назначения контактов микросхемы сигналам схемы

| Сигнал | Номер<br>контакта для<br>набора<br>XC3S200 | Номер контакта<br>для набора<br>Nexys2<br>(XC3E-500) | Назначение                      |

|--------|--------------------------------------------|------------------------------------------------------|---------------------------------|

| CLK    | Т9                                         | В8                                                   | Глобальный сигнал GCLK0(50 МГц) |

| COUNT  | M13                                        | H13                                                  | Сигнал от кнопки 3              |

| RESET  | L14                                        | B18                                                  | Сигнал от кнопки 0              |

| LED[0] | N16                                        | H14                                                  | Сигнал управления сегментом G   |

| LED[1] | F13                                        | J17                                                  | Сигнал управления сегментом F   |

| LED[2] | R16                                        | G14                                                  | Сигнал управления сегментом Е   |

| LED[3] | P15                                        | D16                                                  | Сигнал управления сегментом D   |

| LED[4] | N15                                        | D17                                                  | Сигнал управления сегментом С   |

| LED[5] | G13                                        | F18                                                  | Сигнал управления сегментом В   |

| LED[6] | E14                                        | L18                                                  | Сигнал управления сегментом А   |

| LED[7] | P16                                        | C17                                                  | Сигнал управления сегментом DP  |

| A[0]   | D14                                        | F17                                                  | Сигнал управления анодом 0      |

| A[1]   | G14                                        | H17                                                  | Сигнал управления анодом 1      |

| A[2]   | F14                                        | C18                                                  | Сигнал управления анодом 2      |

| A[3]   | E13                                        | F15                                                  | Сигнал управления анодом 3      |

Задание 6. В редакторе схем САПР ISE WebPack 9.1. собрать модель полученного устройства, включающего схему подавления дребезга, схему управления 7-сегментными индикаторами, 16-разрядный счетчик и схему деления частоты для активизации 7-сегментных индикаторов (библиотечные элементы СВ16СЕ и ВUFGCE). Для использования описаний в составе описаний более высокого уровня необходимо создать для них символы, благодаря чему описания включается в библиотеку. Для этого следует

во вкладке Sources окна Sources выбрать описание проекта, после чего во вкладке Processes окна Processes выбрать ветвь Design Utilities и пункт Create Schematic Symbol.

Созданное описание следует указать в качестве модуля верхнего уровня, для чего необходимо выбрать его в дереве описаний проекта во вкладке Sources окна Sources, после чего в меню Sources выбрать пункт Set as Top Module. Схему основного модуля занести в отчет.

Задание 7. В программе Xilinx PACE создать файл ограничений \*.ucf, в котором назначить внешние выводы сигналам разрабатываемого устройства в соответствии с таблицей 5. Для этого выбрать модуль верхнего уровня в дереве описаний проекта во вкладке Sources окна Sources, после чего во вкладке Processes окна Processes выбрать ветвь User Constraints и пункт Assign Package Pins. В окне редактора РАСЕ назначение контактов выполняется в поле LOC.

Задание 8. В САПР ISE WebPack 9.1 выполнить автоматический синтез технологической схемы, размещение и трассировку полученного устройства на кристалле Spartan3 XC3S200 ft256 (или для Spartan 3E-500 FG320), генерировать файл конфигурации ПЛИС (\*.bin). Для этого в окне Sources выбрать вкладку Sources и в списке Sources For выбрать строку Synthesis/Implementation. После этого в дереве описаний проекта выбрать описание верхнего уровня, а во вкладке Processes окна Processes выбрать ветвь Generate Programming File и пункт Programming File Generation Report.

Занести в отчет общие сведения о результатах проектирования устройства с вкладки Design Summary. Сделать выводы о быстродействии полученного устройства, используя отчет Static Timing Report.

Задание 8. Выполнить программирование макетной ПЛИС Spartan3 отладочного набора XC3S200 или Nexys2. Для этого в окне Sources выбрать вкладку Sources и в списке Sources For выбрать строку Synthesis/Implementation. После этого в дереве описаний проекта выбрать описание верхнего уровня, а во вкладке Processes окна Processes выбрать ветвь Generate Programming File и пункт Configure Device. В результате будет запущен модуль iMPACT. В открывшемся диалоге выбора способа программирования отметить пункт Configure devices using Boundary-Scan и выбрать автоматический способ идентификации. В результате будет определена цепочка, состоящая из ПЛИС и Flash ПЗУ.

После автоматического определения цепочки граничного сканирования по JTAG интерфейсу необходимо запрограммировать ПЛИС XC3S200 (или Spartan 3E-500 FG320). Для этого необходимо указать файл конфигурации ПЛИС (\*.bit), полученный в задании 7, после чего в окне iMPACT Processes меню выбрать пункт Program.

Провести тестирование разработанного устройства. Результаты тестирование представить в отчете.

### Контрольные вопросы

- 1. Назовите основные этапы проектирования цифровых устройств на основе ПЛИС.

- 2. Какой тип автомата (Мили или Мура) реализован в устройстве подавления дребезга.

- 3. Перечислите устройства, входящие в состав отладочного набора XC3S200 или Nexys2.

- 4. Какую информацию содержит файл ограничений \*.ucf.

- 5. Какой стиль описания на VHDL использован в примере описания драйвера 7сегментных индикаторов.

#### Требования к отчету

Отчет должен содержать:

- 6. ФИО студента, номер группы, номер варианта, номер и название лабораторной работы.

- 7. Функциональную схему разрабатываемого устройства

- 8. Диаграмма состояния автомата подавления дребезга

- 9. Заполненные в соответствии с индивидуальным заданием таблицы 2 и 3.

- 10. Карты Карно и результаты минимизации функций сигналов CNT, CNT\_EN, CNT CLR,D1,D0.

- 11. Схему автомата подавления дребезга (скриншот модуля).

- 12. Результаты верификации схемы в ПО Modelsim.

- 13. VHDL код модуля управления семисегментным индикатором

- 14. Схему модуля верхнего уровня проекта (скриншот модуля).

- 15. Результаты верификации проекта на отладочной плате.

#### Список литературы

1. Попов А.Ю. Проектирование цифровых устройств с использованием ПЛИС: Учеб. пособие. — М.: Изд-во МГТУ им. Н.Э. Баумана, 2009.

- 2. Угрюмов Е. П. Цифровая схемотехника: Учеб. Пособие для вузов. 2-е изд., перераб. и доп. СПб.: БХВ-Петербург, 2004. 800 с.: ил.

- 3. Грушвицкий Р. И., Мурсаев А. Х., Угрюмов Е. П. Проектирование систем на микросхемах с программируемой структурой, БХВ-Петербург, 2006, 708 с.

- 4. Spartan-3 FPGA Family: Complete Data Sheet. Xilinx Inc.

- 5. Xilinx ISE Guide (HTML Book). Xilinx Inc.

- 6. Xilinx ISE 9 Software Manuals

- 7. Spartan-3 Starter Kit Board User Guide (<a href="www.digilentinc.com">www.digilentinc.com</a>)

- 8. Nexys 2 Board User Guide (www.digilentinc.com)

- 9. В. Зотов Инструментальный комплект Spartan3 Starter Kit